# Vivado Design Suite

George Matzouranis & Sotiris Totomis CS-220

#### **FPGAs**

A field-programmable gate array (FPGA) is a circuit designed to be configured using hardware description language HDL

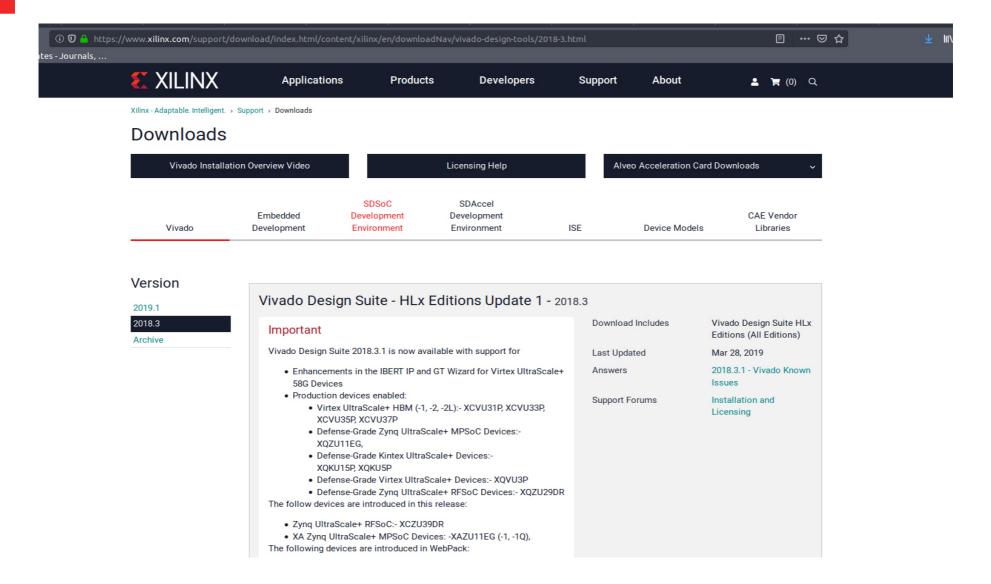

#### Vivado

Produced by Xilinx

- A software suite used for

- 1) Simulation

- 2) Synthesis

of HDL (Hardware Design Language such as SystemVerilog) designs

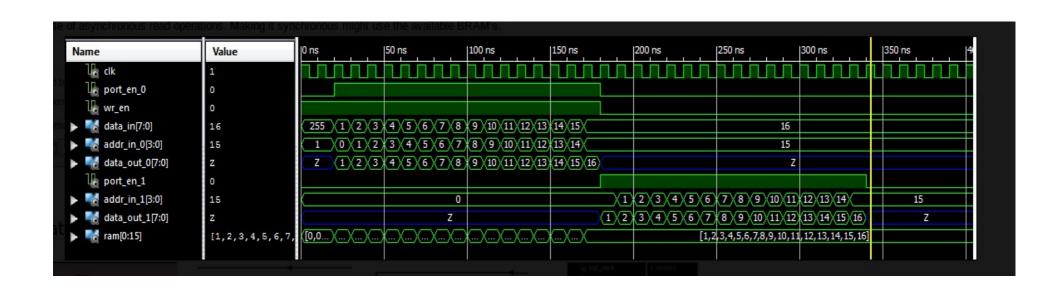

#### Simulation

The simulation of an electronic circuit helps the designer by visualizing the circuit's behavior

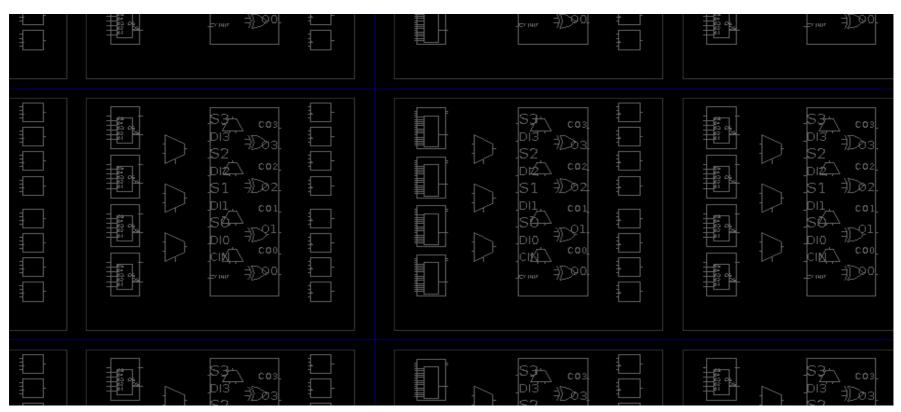

# **Synthesis**

• Synthesis generates LUT-level schematic of the design

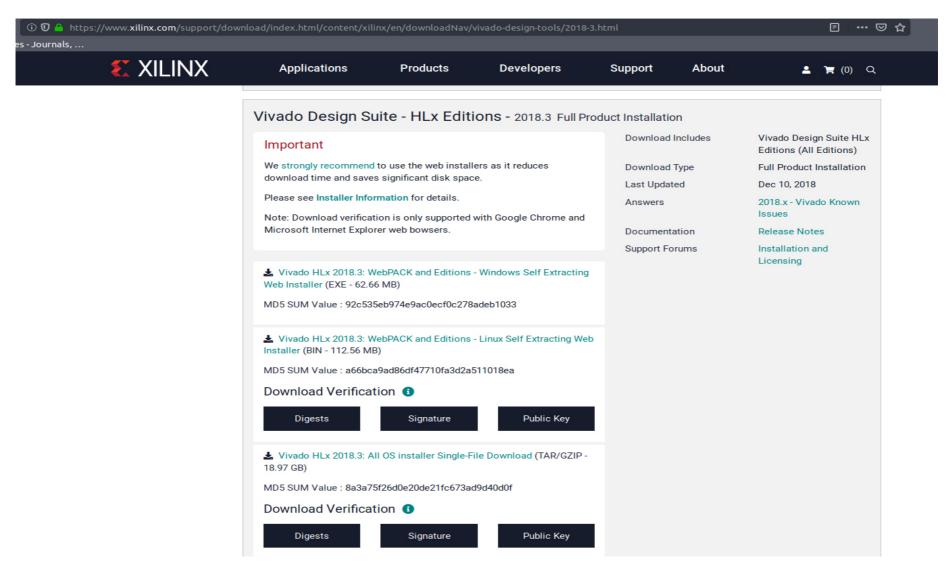

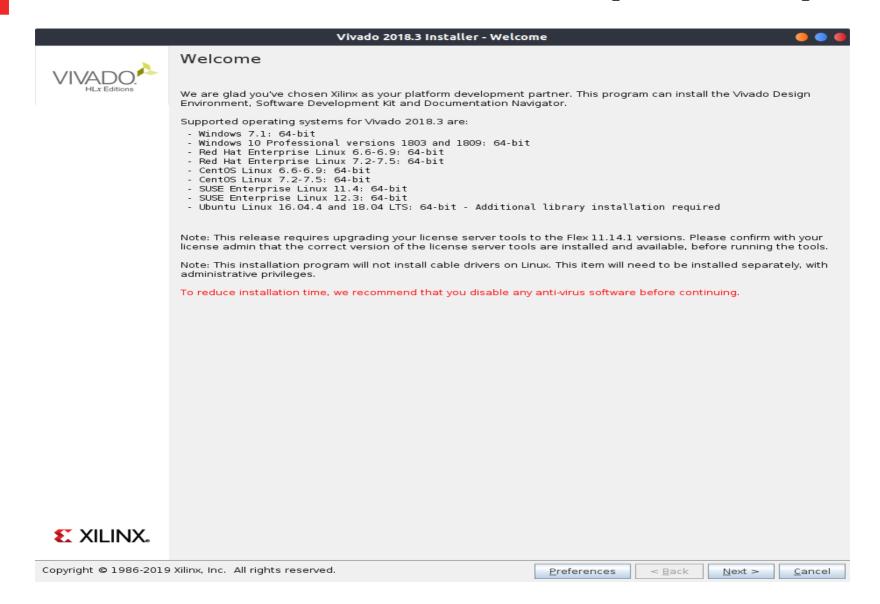

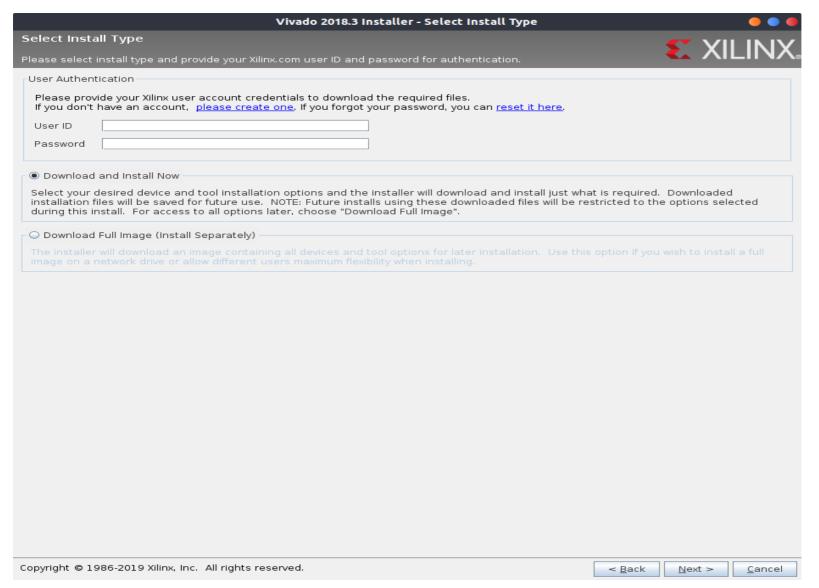

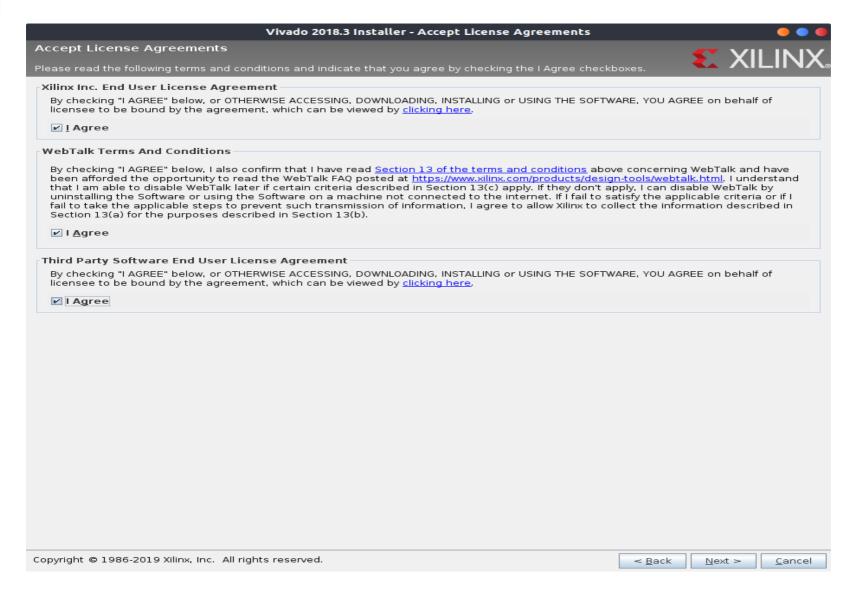

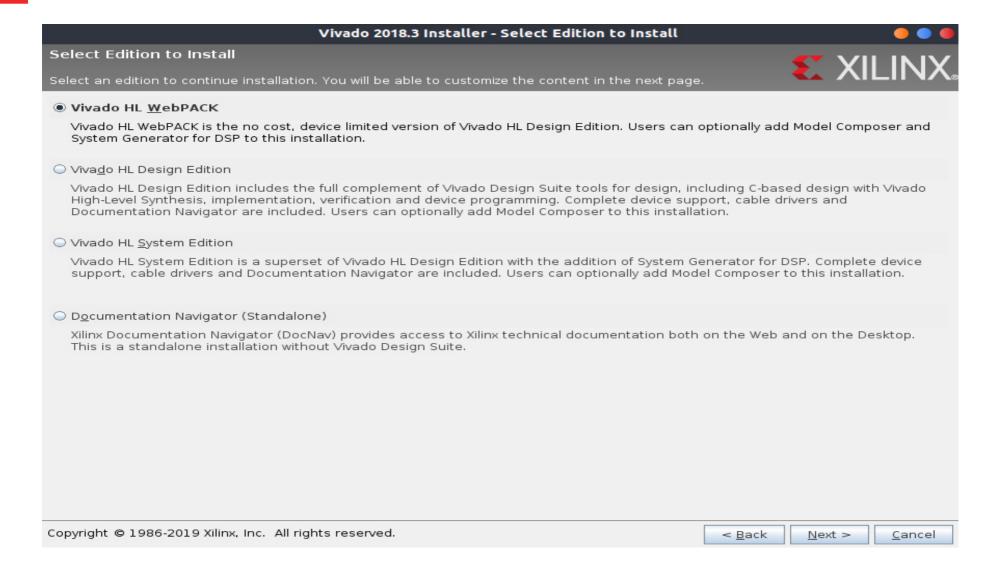

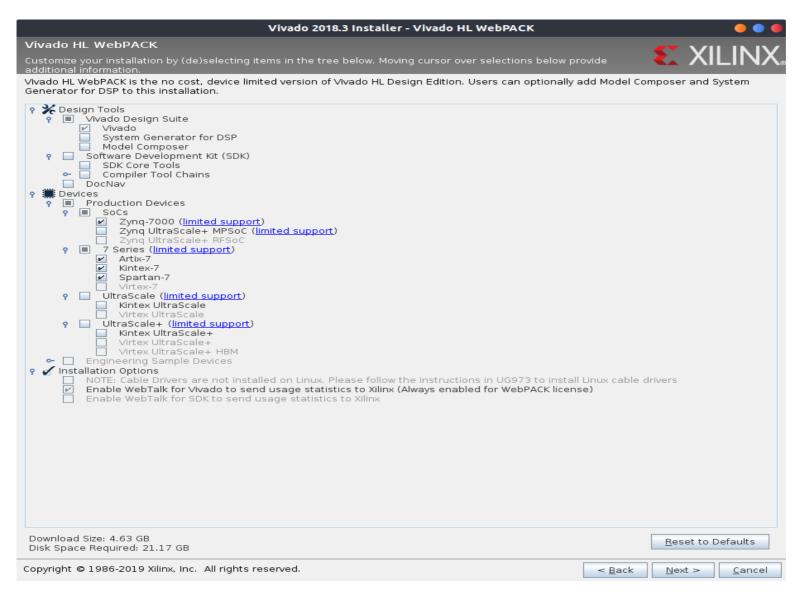

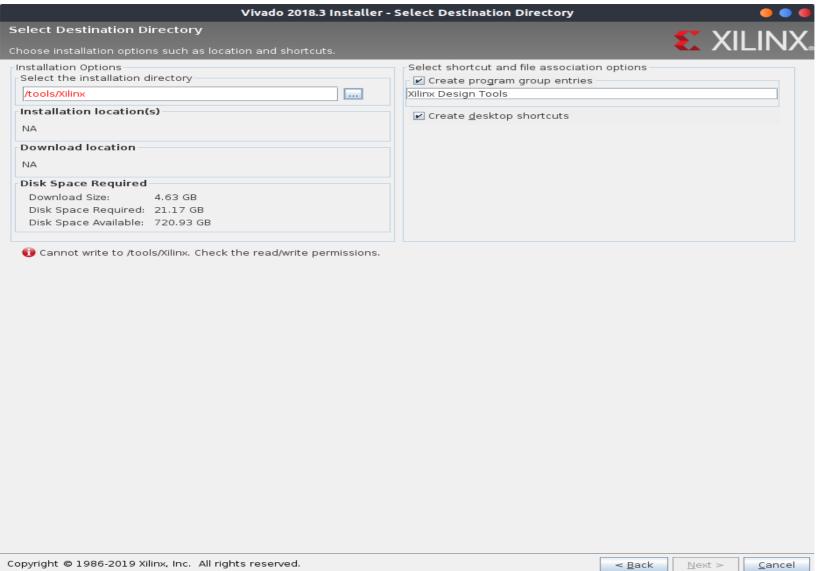

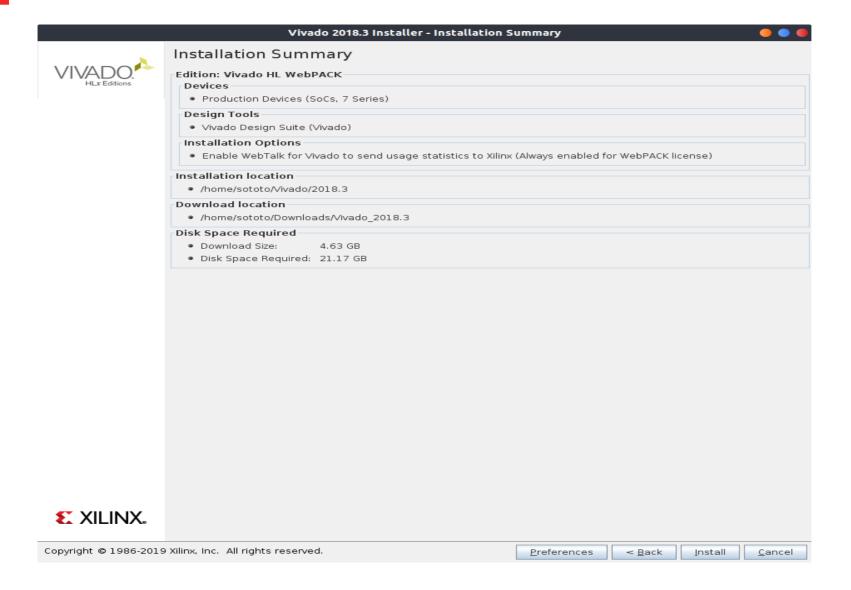

#### **Vivado Installation**

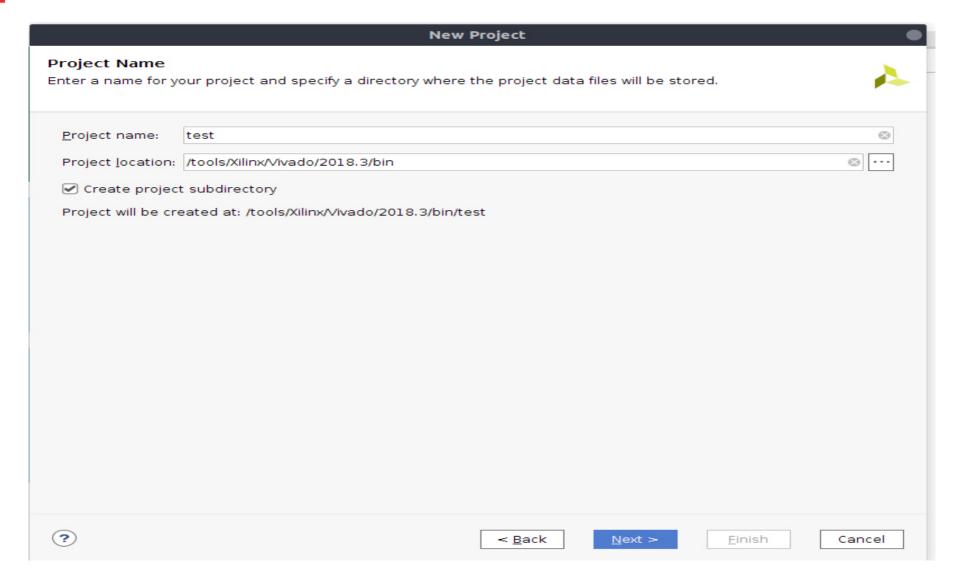

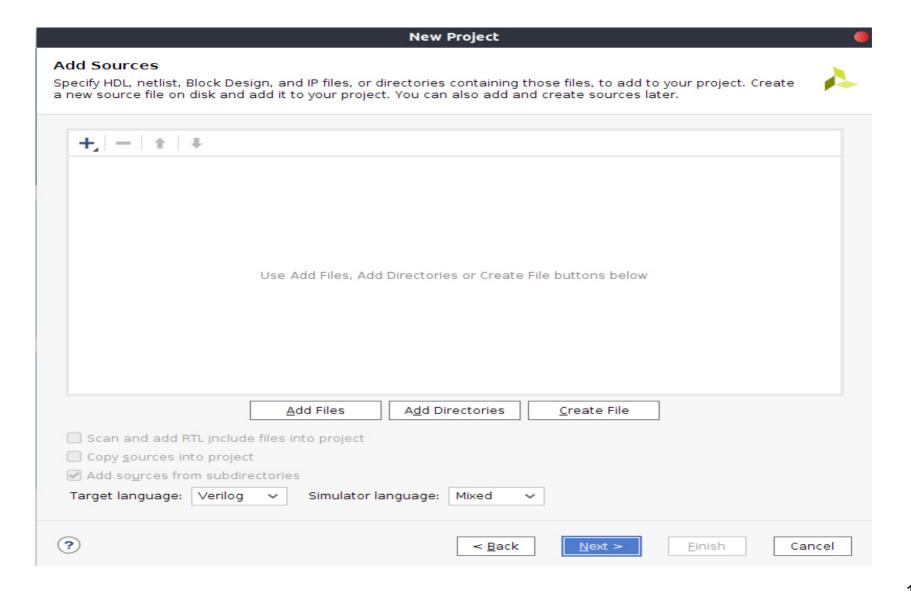

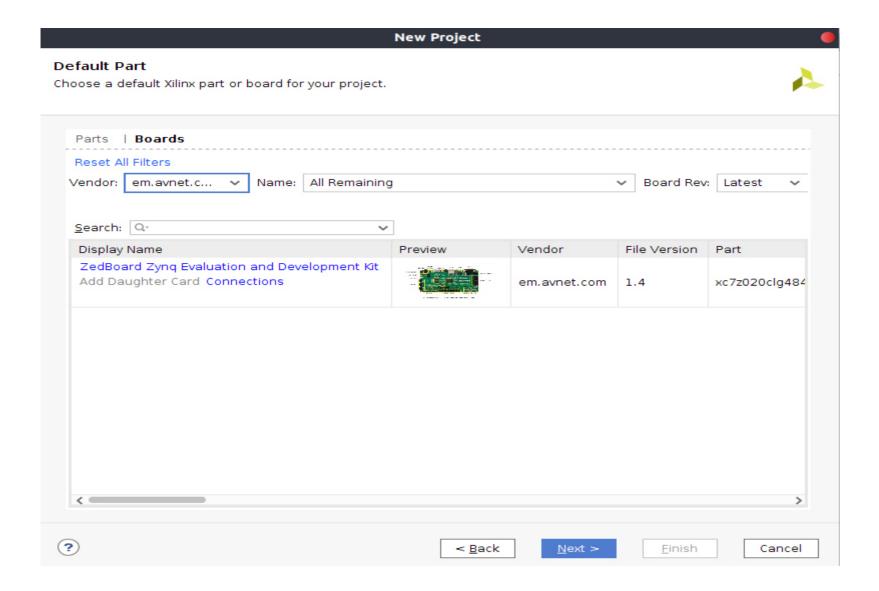

# Creating a project

#### **New Project** Project Type Specify the type of project to create. RTL Project You will be able to add sources, create block designs in IP Integrator, generate IP, run RTL analysis, synthesis, implementation, design planning and analysis. Do not specify sources at this time Post-synthesis Project: You will be able to add sources, view device resources, run design analysis, planning and implementation. Do not specify sources at this time I/O Planning Project Do not specify design sources. You will be able to view part/package resources. Imported Project Create a Vivado project from a Synplify, XST or ISE Project File. Example Project Create a new Vivado project from a predefined template. < Back Next > Finish Cancel

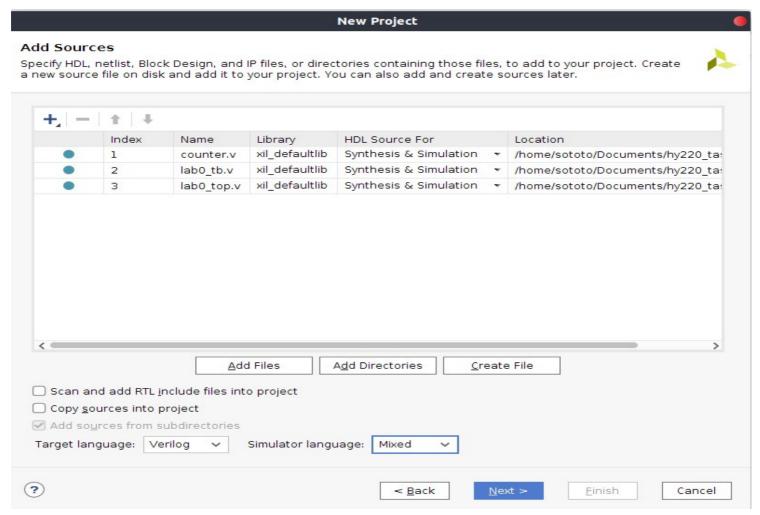

- Wrong!!!

- lab0\_tb.v must be set for simulation only!!!

- Testbenches include non-synthesizable code!!!

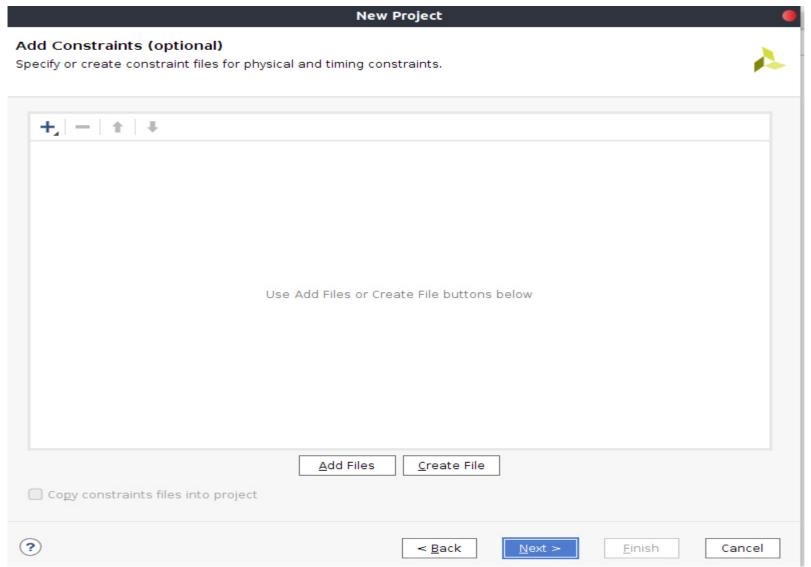

#### **Constraints file**

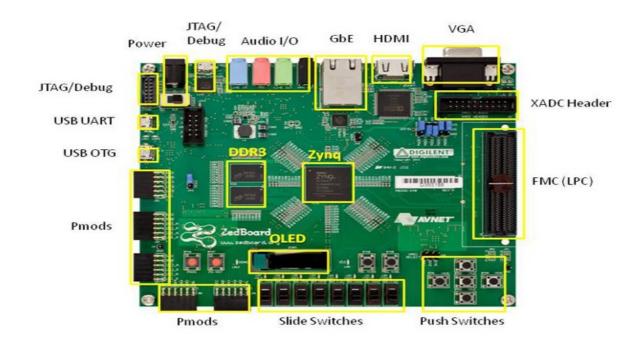

- When programming an FPGA through software such as Xilinx's Vivado, you need to inform the software what physical pins on the FPGA that you plan on using.

- Xilinx Design Constraints file (XDC file)

# Flow Navigator

- Run Simulation

- -Will show the waveform of the design that represents its behavior

- → most bugs can be caught here!!!

- Open Elaborated Design

- -Generates the schematic of your code

- → can be useful when you want to know exactly all and non-trivial connections of the design

# Flow Navigator

- Run Synthesis

- -Will show the corresponding LUT schematic of the selected device

- →Info about timing, utilization and critical paths!!!

- Run Implementation

- -Here the same schematic as before will be showed with the design implemented on it for our selected device

# Flow Navigator

- Generate Bitstream

- -In here the bitstream is generated by the initial design in order to program the selected device

- Open Hardware Manager

- -Open Target to find the connected device

- -Program Device to download the generated bitstream to the connected device!

#### Demo time!!!

Questions...?