# Introduction to hardware design

Sotiris Totomis CS-220 (Spring '24)

### **FPGAs**

- A Field Programmable Gate Array is a re-configurable circuit

- Hardware Description Languages (HDLs)

## Vivado Design Suite

- Developed by Xilinx (now AMD)

- Vivado is suitable for

- Simulation

- Synthesis

of HDL (SystemVerilog) designs

### Simulation

- The simulation of a circuit displays circuit's behavior to hardware (HW) designers

- Why do we need a testbench (TB) for that?

| Name                | Value                          | 0 ns           | 50 ns     | 100 ns        | 150 ns     | 200 ns      | 250 ns                                          | 300 ns                 | 350 ns   |

|---------------------|--------------------------------|----------------|-----------|---------------|------------|-------------|-------------------------------------------------|------------------------|----------|

| 🗓 cik               | 1                              |                |           |               |            |             |                                                 |                        |          |

| 🔓 port_en_0         | 0                              |                |           |               |            |             |                                                 |                        |          |

| Le wr_en            | 0                              |                |           |               |            |             |                                                 |                        | <u>i</u> |

| ▶ 🔩 data_in[7:0]    | 16                             | 255 1/2/3      | 4 5 6 7 8 | 9/10/11/12/13 | 3 14 15    |             | 16                                              |                        |          |

| ▶ 🛃 addr_in_0[3:0]  | 15                             | 1 0 1 2        | 34567     | 8 9 10 11 12  | 2 13 14    |             | 15                                              |                        | <u>i</u> |

| ▶ 🔣 data_out_0[7:0] | z                              | Z (1)(2)(3     | 4 5 6 7 8 | 9/10/11/12/13 | 3 14 15 16 |             | Z                                               |                        |          |

| 🔓 port_en_1         | 0                              |                |           |               |            |             |                                                 |                        |          |

| ▶ 🔣 addr_in_1[3:0]  | 15                             |                | 0         |               |            | 12/3/4/5/6  | 7 8 9 10 11                                     | 12/13/14/              | 15       |

| ▶ 🛃 data_out_1[7:0] | z                              |                | Z         |               |            | 2 3 4 5 6 7 | 8 9 10 11 12                                    | 13/14/15/16/           | Z        |

| 🕨 🛃 ram[0:15]       | [1,2,3,4,5,6,7                 | <b>[0,0</b> )  |           |               |            | [1,         | 2,3,4,5,6,7,8,9,10,1                            | 1, 12, 13, 14, 15, 16] |          |

|                     | State and second contracts and | <b>[0,0</b> )) |           |               |            |             | a second descent film and the second the second |                        |          |

### Synthesis

- Transforms Register Transfer Level (RTL) designs to logic gates

- Look-Up Tables (LUTs)

### **Vivado Installation**

- Dependencies for Linux machines

- sudo apt install libtinfo5

- sudo apt install libncurses5

- Linux installation

- sudo ./xsetup

- Windows installation

- xsetup.exe

| Version                         | We strongly recommend using the latest releases available. |

|---------------------------------|------------------------------------------------------------|

| 2023.2                          | 2021                                                       |

| 2023.1<br>2022.2                | 2021.1                                                     |

| 2022.1<br>Vivado Archive        | 2021.2                                                     |

| ISE Archive                     | 2020                                                       |

| CAE Vendor Libraries<br>Archive | 2020.3                                                     |

|                                 | 2020.2                                                     |

|                                 | 2020.1                                                     |

|                                 | 2019                                                       |

|                                 | 2019.2                                                     |

|                                 | 2019.1                                                     |

|                                 | 2018                                                       |

|                                 | 2018.3                                                     |

|                                 | 2018.2                                                     |

|                                 | 2018.1                                                     |

Public Key

### Vivado Design Suite - HLx Editions - 2018.3 Full Product Installation

### Important

We strongly recommend to use the web installers as it reduces download time and saves significant disk space.

Please see Installer Information for details.

Note: Download verification is only supported with Google Chrome and Microsoft Edge web bowsers.

Livado HLx 2018.3: All OS installer Single-File Download (TAR/GZIP - 18.97 GB)

MD5 SUM Value : 8a3a75f26d0e20de21fc673ad9d40d0f

Download Verification 🚯

Signature

Download IncludesVivado Design Suite HLx<br/>Editions (All Editions)Download TypeFull Product InstallationLast UpdatedDec 10, 2018Answers2018.x - Vivado Known<br/>IssuesDocumentationRelease NotesSupport ForumsInstallation and<br/>Licensing

Vivado 2018.3 Installer - Welcome

### Welcome

We are glad you've chosen Xilinx as your platform development partner. This program can install the Vivado Design Environment, Software Development Kit and Documentation Navigator.

Supported operating systems for Vivado 2018.3 are:

- Windows 7.1: 64-bit

- Windows 10 Professional versions 1803 and 1809: 64-bit

- Red Hat Enterprise Linux 6.6-6.9: 64-bit

- Red Hat Enterprise Linux 7.2-7.5: 64-bit

- CentOS Linux 6.6-6.9: 64-bit

- CentOS Linux 7.2-7.5: 64-bit

- SUSE Enterprise Linux 11.4: 64-bit

- SUSE Enterprise Linux 12.3: 64-bit

- Ubuntu Linux 16.04.4 and 18.04 LTS: 64-bit Additional library installation required

Note: This release requires upgrading your license server tools to the Flex 11.14.1 versions. Please confirm with your license admin that the correct version of the license server tools are installed and available, before running the tools.

Note: This installation program will not install cable drivers on Linux. This item will need to be installed separately, with administrative privileges.

To reduce installation time, we recommend that you disable any anti-virus software before continuing.

Vivado 2018.3 Installer - Accept License Agreements

### Accept License Agreements

Please read the following terms and conditions and indicate that you agree by checking the I Agree checkboxes.

### Xilinx Inc. End User License Agreement

By checking "I AGREE" below, or OTHERWISE ACCESSING, DOWNLOADING, INSTALLING or USING THE SOFTWARE, YOU AGREE on behalf of licensee to be bound by the agreement, which can be viewed by <u>clicking here</u>.

🖌 🛛 🖉 🖌 🖌

WebTalk Terms And Conditions-

By checking "I AGREE" below, I also confirm that I have read <u>Section 13 of the terms and conditions</u> above concerning WebTalk and have been afforded the opportunity to read the WebTalk FAQ posted at <u>https://www.xilinx.com/products/design-tools/webtalk.html</u>. I understand that I am able to disable WebTalk later if certain criteria described in Section 13(c) apply. If they don't apply, I can disable WebTalk by uninstalling the Software or using the Software on a machine not connected to the internet. If I fail to satisfy the applicable criteria or if I fail to take the applicable steps to prevent such transmission of information, I agree to allow Xilinx to collect the information described in Section 13(a) for the purposes described in Section 13(b).

✓ I <u>Agree</u>

Third Party Software End User License Agreement

By checking "I AGREE" below, or OTHERWISE ACCESSING, DOWNLOADING, INSTALLING or USING THE SOFTWARE, YOU AGREE on behalf of licensee to be bound by the agreement, which can be viewed by <u>clicking here</u>.

### 🖌 l Agree

### Vivado 2018.3 Installer - Select Edition to Install

### Select Edition to Install

Select an edition to continue installation. You will be able to customize the content in the next page.

### Vivado HL <u>WebPACK</u>

Vivado HL WebPACK is the no cost, device limited version of Vivado HL Design Edition. Users can optionally add Model Composer and System Generator for DSP to this installation.

### Vivado HL Design Edition

Vivado HL Design Edition includes the full complement of Vivado Design Suite tools for design, including C-based design with Vivado High-Level Synthesis, implementation, verification and device programming. Complete device support, cable drivers and Documentation Navigator are included. Users can optionally add Model Composer to this installation.

### Vivado HL System Edition

Vivado HL System Edition is a superset of Vivado HL Design Edition with the addition of System Generator for DSP. Complete device support, cable drivers and Documentation Navigator are included. Users can optionally add Model Composer to this installation.

### Documentation Navigator (Standalone)

Xilinx Documentation Navigator (DocNav) provides access to Xilinx technical documentation both on the Web and on the Desktop. This is a standalone installation without Vivado Design Suite.

| Copyright © 1986-2019 Xilinx, Inc. All rights reserved. | < <u>B</u> ack | <u>N</u> ext > | <u>C</u> ancel |

|---------------------------------------------------------|----------------|----------------|----------------|

|---------------------------------------------------------|----------------|----------------|----------------|

🐮 XILIN

### Vivado 2018.3 Installer - Vivado HL WebPACK

### Vivado HL WebPACK

Customize your installation by (de)selecting items in the tree below. Moving cursor over selections below provide additional information.

Vivado HL WebPACK is the no cost, device limited version of Vivado HL Design Edition. Users can optionally add Model Composer and System Generator for DSP to this installation.

12 / 30

| Vivado 2018.3 Installer - S                                                                      | Select Destination Directory                                                                                                            |                 |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Select Destination Directory                                                                     |                                                                                                                                         | <b>E</b> XILINX |

| Choose installation options such as location and shortcuts.                                      |                                                                                                                                         |                 |

| Installation Options Select the installation directory /tools/Xilinx Installation location(s) NA | Select shortcut and file association options<br>Create program group entries<br>Xilinx Design Tools<br>Create <u>d</u> esktop shortcuts |                 |

| Download location<br>NA<br>Disk Space Required<br>Download Size: 4 63 68                         | ected directory<br>ged you must<br>allation with sudo!                                                                                  |                 |

🕕 Cannot write to /tools/Xilinx. Check the read/write permissions.

Cancel

### Vivado 2018.3 Installer - Installation Summary

### Installation Summary

### Edition: Vivado HL WebPACK

Production Devices (SoCs, 7 Series)

### Design Tools

Devices

Vivado Design Suite (Vivado)

### Installation Options

• Enable WebTalk for Vivado to send usage statistics to Xilinx (Always enabled for WebPACK license)

### Installation location

/home/sototo/Vivado/2018.3

### Download location

/home/sototo/Downloads/Vivado\_2018.3

### Disk Space Required

- Download Size: 4.63 GB

- Disk Space Required: 21.17 GB

### **E**XILINX.

<u>C</u>ancel

# Sourcing settings to path

- Before executing Vivado through command line you have to source its settings

- cd installation\_path/Xilinx/Vivado/2018.3

- source settings64.sh

- After this you can execute Vivado GUI by typing

- vivado

### **Creating a project**

File Flow Tools Window Help Q- Quick Access

### Quick Start

Create Project > Open Project > Open Example Project

### Tasks

Manage IP > Open Hardware Manager > Xilinx Tcl Store >

### Learning Center

Documentation and Tutorials > Quick Take Videos > Release Notes Guide >

### Recent Projects

lab0\_intro /home/sototo/Documents/hy220\_tas/lab0\_intro

lab0\_intro /tools/Xilinx/Vivado/2018.3/bin/lab0\_intro

test\_SystemVerilog /home/sototo/Documents/test\_SystemVerilog

|                                     | New Project                                                                      | •      |

|-------------------------------------|----------------------------------------------------------------------------------|--------|

| Project Name<br>Enter a name for ye | our project and specify a directory where the project data files will be stored. | ~      |

| Project name:<br>Project location:  | test<br>/tools/Xilinx/Vivado/2018.3/bin                                          |        |

| 3                                   | < <u>B</u> ack <u>N</u> ext > <u>F</u> inish                                     | Cancel |

### New Project

### Project Type Specify the type of project to create. BTL Project You will be able to add sources, create block designs in IP Integrator, generate IP, run RTL analysis, synthesis, implementation, design planning and analysis. Do not specify sources at this time Post-synthesis Project: You will be able to add sources, view device resources, run design analysis, planning and implementation. Do not specify sources at this time J/O Planning Project Do not specify design sources. You will be able to view part/package resources. Imported Project Create a Vivado project from a Synplify, XST or ISE Project File. Example Project Create a new Vivado project from a predefined template.

| <ul> <li>?</li> </ul> | < <u>B</u> ack | <u>N</u> ext > | <u>F</u> inish | Cancel |

|-----------------------|----------------|----------------|----------------|--------|

### New Project

### Add Sources

Specify HDL, netlist, Block Design, and IP files, or directories containing those files, to add to your project. Create a new source file on disk and add it to your project. You can also add and create sources later.

| $ \mathbf{+}_{\mathbf{z}}  =  \mathbf{+}  \mathbf{+}$       |

|-------------------------------------------------------------|

|                                                             |

|                                                             |

| Use Add Files. Add Directories or Create File buttons below |

| Use Add Files, Add Directories of create File buttons below |

|                                                             |

|                                                             |

| Add Files Add Directories Create File                       |

| Scan and add RTL include files into project                 |

| Copy <u>s</u> ources into project                           |

| Add sources from subdirectories                             |

| Target language: Verilog 🗸 Simulator language: Mixed 🗸      |

| ? < <u>Back</u> <u>Next</u> > <u>Finish</u> Cancel          |

|                              |                                 |                                    | 1                                     | New Project              | ۲                                                   |

|------------------------------|---------------------------------|------------------------------------|---------------------------------------|--------------------------|-----------------------------------------------------|

| Add Sourc                    | es                              |                                    |                                       |                          |                                                     |

| Specify HDL,<br>a new source | netlist, Bloc<br>e file on disk | k Design, and I<br>and add it to g | P files, or direc<br>your project. Yo | ou can also add          | his is a usual mistake!<br>are for Simulation Only! |

| $ +_{i}  =$                  | ++                              |                                    |                                       |                          | But why?                                            |

|                              | Index                           | Name                               | Library                               | HDL Source For           |                                                     |

| •                            | 1                               | counter.v                          | xil_defaultlib                        | Synthesis & Simulation   | nome/sototo/Documents/hy220_ta:                     |

| •                            | 2                               | lab0_tb.v                          | xil_defaultlib                        | Synthesis & Simulation   | /home/sototo/Documents/hy220_ta:                    |

| •                            | 3                               | lab0_top.v                         | xil_defaultlib                        | Synthesis & Simulation 👻 | /home/sototo/Documents/hy220_ta:                    |

| <                            |                                 | Add                                | l Files                               | A <u>d</u> d Directories | te File                                             |

| 🗌 Copy <u>s</u> o            | urces into p<br>irces from s    | ubdirectories                      | o project<br>Simulator langu          | uage: Mixed 🗸            |                                                     |

| ?                            |                                 |                                    |                                       | < <u>B</u> ack           | ext > <u>F</u> inish Cancel                         |

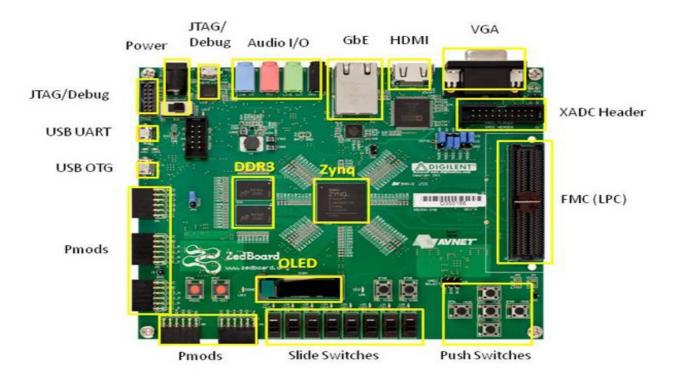

# Xilinx Constraints files (XDC)

- FPGAs include some physical pins such as buttons, LEDs, etc.

- If we are planning on using these pins we must inform Vivado to associate them with our HW designs

- All XDC files are provided

### Add Constraints (optional)

Specify or create constraint files for physical and timing constraints.

| +,   -   +   +                      |                                            |  |

|-------------------------------------|--------------------------------------------|--|

|                                     |                                            |  |

|                                     |                                            |  |

|                                     | Use Add Files or Create File buttons below |  |

|                                     |                                            |  |

|                                     |                                            |  |

|                                     | Add Files <u>C</u> reate File              |  |

| Copy constraints files into project |                                            |  |

| ?)                                  | < <u>B</u> ack                             |  |

|                                                                               | New Project                      |              |              |              |

|-------------------------------------------------------------------------------|----------------------------------|--------------|--------------|--------------|

| efault Part<br>noose a default Xilinx part or board for your project.         |                                  |              |              |              |

| Parts   Boards                                                                |                                  |              |              |              |

| Reset All Filters                                                             |                                  |              |              |              |

| Vendor: em.avnet.c v Name: All Remainin                                       | g                                | 9            | ✓ Board Rev: | Latest 🗸     |

| Search: Q-                                                                    | •                                |              |              |              |

| Display Name                                                                  | Preview                          | Vendor       | File Version | Part         |

| ZedBoard Zynq Evaluation and Development Kit<br>Add Daughter Card Connections |                                  | em.avnet.com | 1.4          | xc7z020clg48 |

|                                                                               | Recting the second of the second |              |              |              |

|                                                                               |                                  |              |              |              |

|                                                                               |                                  |              |              |              |

|                                                                               |                                  |              |              |              |

|                                                                               |                                  |              |              |              |

|                                                                               |                                  |              |              |              |

|                                                                               |                                  |              |              |              |

|                                                                               |                                  |              |              | >            |

|                                                                               |                                  |              |              | >            |

### **Flow Navigator**

- Run Simulation

- Shows the waveform of the design that represents its behavior

- Main debugging routine

- Open Elaborated Design

- Generates and displays the schematic of your design

### **Flow Navigator**

- Run Synthesis

- Shows the corresponding LUT schematic of the selected device

- Displays info about timing, utilization and critical paths

- Run Implementation

- Implements your design and places it on the selected FPGA device

### **Flow Navigator**

- Generate bitstream

- Generates the bitstream, which is used to program the FPGA

- Open Hardware Manager

- Finds the connected device

- Programs Device to download the generated bitstream to the connected device

### Work remotely - connect

- Instead of working on your own machine, you can run simulations on Debian machines.

- Interactively through command line

- Interactively with GUI through ssh display forwarding (ssh -X <hostname>)

## Work remotely - flow

- cp -r ~hy220/tools/example .

- cd example

- source setup.sh

- export HY220\_SIMULATOR=[verilator,vivado,icarus]

- Work interactively

- make

- make gwaves (after make)

- It opens the generated wave files with gtkwave viewer

## Work remotely - your files

- mkdir project\_file

- cp Makefile, setup.sh (from example)

- Edit Makefile (SRCS, TOP\_MODULE)

- Repeat compilation flow

# Switch to Vivado for demo